音源ICの使い方一覧へ

AY-3-8910(PSG)・SSGの使い方➀

注意:このサイトの内容を鵜呑みにし、事故や損失を招いた場合でも当方は一切の責任は負いかねます。自己責任でお願いします。

AY-3-8910は矩形波3出力+ノイズのPSG音源ICです。

この音源ICは家庭用のテレビゲーム用IC 「GIMINI 8900」 シリーズの1つとして開発されたようです。

「GIMINI 8900」シリーズの中でもAY-3-8910は、ゲーム機やPC、その他機器にこぞって使われていました。

そのため、AY-3-8910はもちろん、セカンドソース品や互換品が今でも多く出回っており、入手は比較的容易です。

特にYAMAHAはAY-3-8910をもとにした音源ICをいくつか作っていました。

・YM2149 (SSG) AY-3-8910のピンコンパチブル品(エンベロープ分解能も増やした)

・YM3439 (SSGC) YM2149のCMOS品

・YMZ284 (SSGL) YM3439からI/Oポートを省きサウンド出力を1つにまとめたもの(バス制御信号はCS, WR, A0)

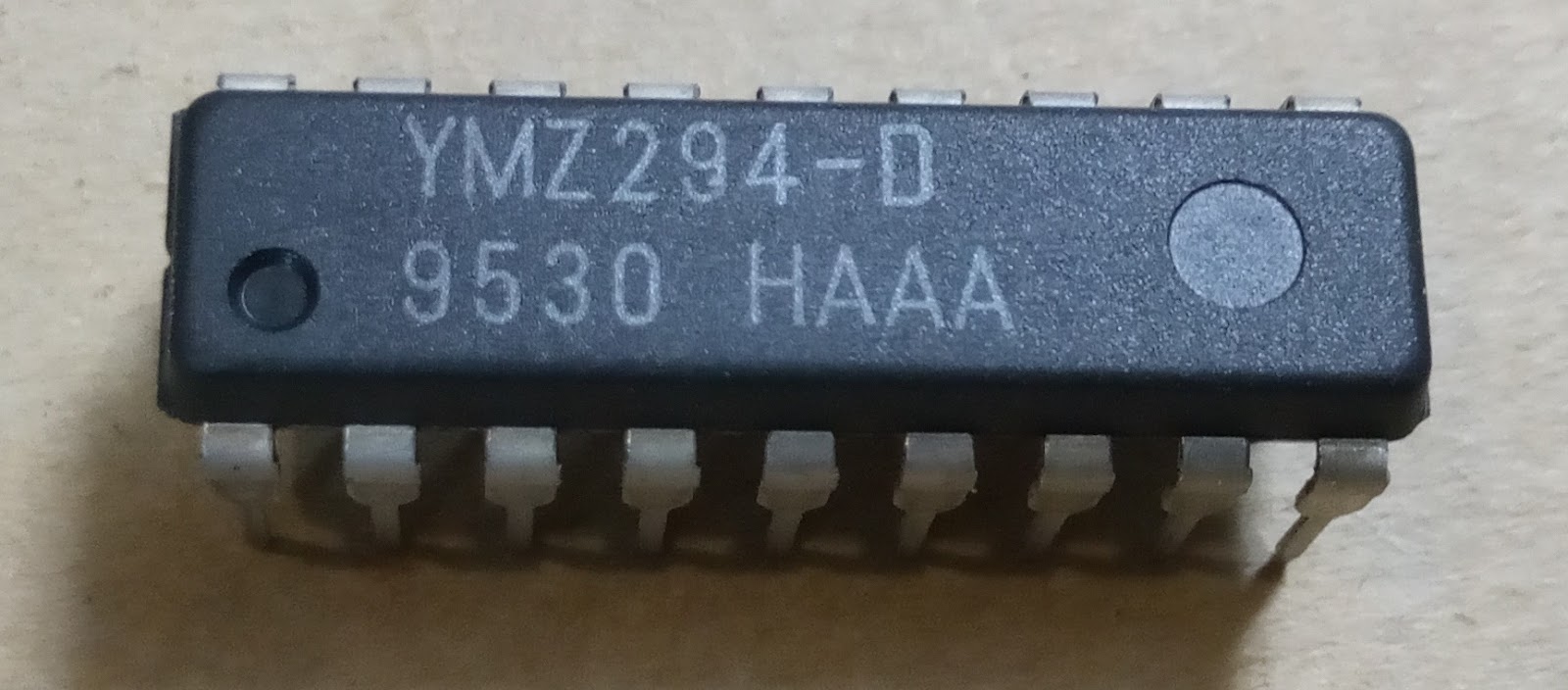

・YMZ294 (SSGLP) YMZ284にマスタークロック周波数4MHz/6MHzの選択とテストピンを追加したもの(バス制御信号はCS, WR, A0)

また、YM2149とほかの音源や周辺ロジックを含めたものも多数あります。

※この記事では以下の音源ICの詳細な説明はしないので注意してください。

・S3527 (MSX SYSTEM)

・S1985 (MSX SYSTEMⅡ)

・YMZ261 (SSGP) YM2149とPCMを内蔵シーケンサで自動演奏できるようにしたもの(ROM内蔵)

・YMZ285 (SSGP2) YMZ261の2倍の演奏データROM容量をもつもの(一応音は出せる)

・YMZ710 (SSGP3) 詳細不明

・YMZ705 (SSGS) YM2149 2つ分とADPCMを内蔵シーケンサで自動演奏できるようにしたもの(外付けROM最大8Mbit)

・YMZ732 (SSGS2) YMZ705の外付けROM最大容量を64Mbitにしたもの

・YMZ771 (SSGS3) YM2149 2つ分とAMMを内蔵シーケンサで自動演奏できるようにしたもの(外付けROM最大256Mbit)

など…

AY-3-8910にはI/Oポートを省いたAY-3-8912やAY-3-8913などもあります。

2023年現在、各種オークションサイトなどでこれらの音源ICの新古品や中古を容易に入手することができます。

特にYMZ294 (SSGLP)、YMZ771 (SSGS3)、YMZ285 (SSGP2)あたりは秋月電子でも入手できます。

ただ、YMZ294はそこそこ人気が高く在庫がもう切れてしまうかもしれません。

YMZ771は、SSGが2系統入りで価格が控えめなのでおすすめではありますが、QFPパッケージなので上級者向けです。

YMZ285は、テストモードで使用することで任意の音程を出すことができます。在庫もそこそこあるのでYMZ294の代替としては良いのかもしれません。

・AY-3-8910の特徴

・同時発音数 : 3

・ハードウェアエンベロープ

・ノイズジェネレータ

・AY-3-8910のブロック図

AY-3-8910のデータシートより抜粋

・ピン配置

AY-3-8910、AY-3-8912、AY-3-8913、YM2149、YMZ284、YMZ294のピン配置を示します。

YM3439はYM2149と同じなので省きます。

・AY-3-8910

| ピン番号 | 名称 | I/O | 機能 | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | Vss(GND) | - | グランド端子です。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 2 | N.C. | - | 未接続 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 3 | ANALOG CHANNEL B | O | チャンネルBのトーン出力端子です。 電流加算DACによる吐き出し電流出力と思われます。 他のチャンネルのトーン出力端子をそのまま接続してミキシングすることができます。 内部の出力部は15個のNchMOSFETをパラレル接続し、16段階の音量値ごとにドライブするMOSFETを選択しているようです。 対象のMOSFETがONした時に流れる電流値が 他のMOSFETがONした時に流れる電流値と異なるように設計されています。 この15個のMOSFETのドレインはVddに接続されています。 ソースが出力となっているので、出力電圧の状態によってはDACの直線性が悪くなる可能性があります。 ですので、AY-3-8910のデータシート内のFig.6のようなオペアンプを使ったI/V変換をすると良いでしょう。 AY-3-8913の場合、Fig.6の回路の最大出力電流は2000μAとなります。AY-3-8910の場合は不明ですが、近い値となると思います。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 4 | ANALOG CHANNEL A | O | チャンネルAのトーン出力端子です。 3番ピンの「ANALOG CHANNEL B」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 5 | N.C. | - | 未接続 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 6 | IOB7 | I/O | 汎用I/Oポート端子です。 レジスタ$7のbit7「IOB」が0のとき入力、1のとき出力となります。 このポートが入力に設定されているとき、レジスタ$Fの対象ビットにこの端子の状態がセットされます。 このポートが出力に設定されているとき、レジスタ$Fの対象ビットの状態がこの端子に反映されます。 これらの端子にはプルアップ抵抗が内蔵されています。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 7 | IOB6 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 8 | IOB5 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 9 | IOB4 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 10 | IOB3 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 11 | IOB2 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 12 | IOB1 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 13 | IOB0 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 14 | IOA7 | I/O | 汎用I/Oポート端子です。 レジスタ$7のbit6「IOA」が0のとき入力、1のとき出力となります。 このポートが入力に設定されているとき、レジスタ$Eの対象ビットにこの端子の状態がセットされます。 このポートが出力に設定されているとき、レジスタ$Eの対象ビットの状態がこの端子に反映されます。 これらの端子にはプルアップ抵抗が内蔵されています。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 15 | IOA6 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 16 | IOA5 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 17 | IOA4 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 18 | IOA3 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 19 | IOA2 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 20 | IOA1 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 21 | IOA0 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 22 | CLOCK | I | マスタークロック入力端子です。 最低1MHz、最大で2MHzまでのクロックを入力できます。 AY-3-8913のみ最大で2.5MHzまでのクロックを入力できます。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 23 | ~RESET | I | リセット端子です。 この端子がLの期間、内部レジスタを初期化します。 この端子にはプルアップ抵抗が内蔵されています。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 24 | ~A9 | I | チップセレクト端子です。 この端子がLかつ25番ピンの「A8」がHの期間に、27番ピンの「BDIR」の説明にある条件の時、内部のレジスタに対して書き込み・読み込みができます。 この端子にはプルダウン抵抗が内蔵されています。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 25 | A8 | I | チップセレクト端子です。 この端子がHかつ24番ピンの「~A9」がLの期間に、27番ピンの「BDIR」の説明にある条件の時、内部のレジスタに対して書き込み・読み込みができます。 この端子にはプルアップ抵抗が内蔵されています。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 26 | TEST 2 | I | テスト用端子です。 詳細不明です。 通常は開放にしておきます。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 27 | BDIR | I | バスコントロール端子です。 28番ピンの「BC2」と29番ピンの「BC1」とともに使用します。 25番ピンの「A8」がHかつ24番ピンの「~A9」がLの場合に以下の操作ができます。

[AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 28 | BC2 | I | バスコントロール端子です。 27番ピンの「BDIR」と29番ピンの「BC1」とともに使用します。 27番ピンの「BDIR」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 29 | BC1 | I | バスコントロール端子です。 27番ピンの「BDIR」と28番ピンの「BC2」とともに使用します。 27番ピンの「BDIR」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 30 | DA7 | I/O | データ・アドレスバス端子です。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 31 | DA6 | I/O | データ・アドレスバス端子です。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 32 | DA5 | I/O | データ・アドレスバス端子です。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 33 | DA4 | I/O | データ・アドレスバス端子です。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 34 | DA3 | I/O | データ・アドレスバス端子です。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 35 | DA2 | I/O | データ・アドレスバス端子です。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 36 | DA1 | I/O | データ・アドレスバス端子です。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 37 | DA0 | I/O | データ・アドレスバス端子です。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 38 | ANALOG CHANNEL C | O | チャンネルCのトーン出力端子です。 3番ピンの「ANALOG CHANNEL B」に説明があるので、そちらを参照してください。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 39 | TEST 1 | O | テスト用端子です。 詳細は不明ですが、エンベロープ用クロックが出力されていると思われます。 通常は開放にしておきます。 [AY-3-8910] |

||||||||||||||||||||||||||||||||||||

| 40 | Vcc(+5V) | - | 電源端子です。 +5Vの電源を用意してください。 [AY-3-8910] |

・AY-3-8912

| ピン番号 | 名称 | I/O | 機能 | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | ANALOG CHANNEL C | O | チャンネルCのトーン出力端子です。 電流加算DACによる吐き出し電流出力と思われます。 他のチャンネルのトーン出力端子をそのまま接続してミキシングすることができます。 内部の出力部は15個のNchMOSFETをパラレル接続し、16段階の音量値ごとにドライブするMOSFETを選択しているようです。 対象のMOSFETがONした時に流れる電流値が 他のMOSFETがONした時に流れる電流値と異なるように設計されています。 この15個のMOSFETのドレインはVddに接続されています。 ソースが出力となっているので、出力電圧の状態によってはDACの直線性が悪くなる可能性があります。 ですので、AY-3-8910のデータシート内のFig.6のようなオペアンプを使ったI/V変換をすると良いでしょう。 AY-3-8913の場合、Fig.6の回路の最大出力電流は2000μAとなります。AY-3-8910の場合は不明ですが、近い値となると思います。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 2 | TEST 1 | O | テスト用端子です。 詳細は不明ですが、エンベロープ用クロックが出力されていると思われます。 通常は開放にしておきます。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 3 | Vcc(+5V) | - | 電源端子です。 +5Vの電源を用意してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 4 | ANALOG CHANNEL B | O | チャンネルBのトーン出力端子です。 1番ピンの「ANALOG CHANNEL C」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 5 | ANALOG CHANNEL A | O | チャンネルBのトーン出力端子です。 1番ピンの「ANALOG CHANNEL C」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 6 | Vss(GND) | - | グランド端子です。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 7 | IOA7 | I/O | 汎用I/Oポート端子です。 レジスタ$7のbit6「IOA」が0のとき入力、1のとき出力となります。 このポートが入力に設定されているとき、レジスタ$Eの対象ビットにこの端子の状態がセットされます。 このポートが出力に設定されているとき、レジスタ$Eの対象ビットの状態がこの端子に反映されます。 これらの端子にはプルアップ抵抗が内蔵されています。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 8 | IOA6 | I/O | 汎用I/Oポート端子です。 7番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 9 | IOA5 | I/O | 汎用I/Oポート端子です。 7番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 10 | IOA4 | I/O | 汎用I/Oポート端子です。 7番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 11 | IOA3 | I/O | 汎用I/Oポート端子です。 7番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 12 | IOA2 | I/O | 汎用I/Oポート端子です。 7番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 13 | IOA1 | I/O | 汎用I/Oポート端子です。 7番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 14 | IOA0 | I/O | 汎用I/Oポート端子です。 7番ピンの「IOA7」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 15 | CLOCK | I | マスタークロック入力端子です。 最低1MHz、最大で2MHzまでのクロックを入力できます。 AY-3-8913のみ最大で2.5MHzまでのクロックを入力できます。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 16 | ~RESET | I | リセット端子です。 この端子がLの期間、内部レジスタを初期化します。 この端子にはプルアップ抵抗が内蔵されています。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 17 | A8 | I | チップセレクト端子です。 この端子がHの期間に、18番ピンの「BDIR」の説明にある条件の時、内部のレジスタに対して書き込み・読み込みができます。 この端子にはプルアップ抵抗が内蔵されています。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 18 | BDIR | I | バスコントロール端子です。 19番ピンの「BC2」と20番ピンの「BC1」とともに使用します。 17番ピンの「A8」がHの場合に以下の操作ができます。

[AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 19 | BC2 | I | バスコントロール端子です。 18番ピンの「BDIR」と20番ピンの「BC1」とともに使用します。 18番ピンの「BDIR」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 20 | BC1 | I | バスコントロール端子です。 18番ピンの「BDIR」と19番ピンの「BC2」とともに使用します。 18番ピンの「BDIR」に説明があるので、そちらを参照してください。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 21 | DA7 | I/O | データ・アドレスバス端子です。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 22 | DA6 | I/O | データ・アドレスバス端子です。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 23 | DA5 | I/O | データ・アドレスバス端子です。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 24 | DA4 | I/O | データ・アドレスバス端子です。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 25 | DA3 | I/O | データ・アドレスバス端子です。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 26 | DA2 | I/O | データ・アドレスバス端子です。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 27 | DA1 | I/O | データ・アドレスバス端子です。 [AY-3-8912] |

||||||||||||||||||||||||||||||||||||

| 28 | DA0 | I/O | データ・アドレスバス端子です。 [AY-3-8912] |

・AY-3-8913

| ピン番号 | 名称 | I/O | 機能 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | Vss(GND) | - | グランド端子です。 [AY-3-8913] |

|||||||||||||||

| 2 | BDIR | I | バスコントロール端子です。 29番ピンの「BC1」とともに使用します。 24番ピンの「~CHIP SELECT」がL かつ 23番ピンの「A8」がH かつ 22番ピンの「~A9」がLの場合に以下の操作ができます。

[AY-3-8913] |

|||||||||||||||

| 3 | BC1 | I | バスコントロール端子です。 2番ピンの「BDIR」とともに使用します。 2番ピンの「BDIR」に説明があるので、そちらを参照してください。 [AY-3-8913] |

|||||||||||||||

| 4 | DA7 | I/O | データ・アドレスバス端子です。 [AY-3-8913] |

|||||||||||||||

| 5 | DA6 | I/O | データ・アドレスバス端子です。 [AY-3-8913] |

|||||||||||||||

| 6 | DA5 | I/O | データ・アドレスバス端子です。 [AY-3-8913] |

|||||||||||||||

| 7 | DA4 | I/O | データ・アドレスバス端子です。 [AY-3-8913] |

|||||||||||||||

| 8 | DA3 | I/O | データ・アドレスバス端子です。 [AY-3-8913] |

|||||||||||||||

| 9 | DA2 | I/O | データ・アドレスバス端子です。 [AY-3-8913] |

|||||||||||||||

| 10 | DA1 | I/O | データ・アドレスバス端子です。 [AY-3-8913] |

|||||||||||||||

| 11 | DA0 | I/O | データ・アドレスバス端子です。 [AY-3-8913] |

|||||||||||||||

| 12 | TEST OUT | O? | テスト用端子です。 詳細不明です。 通常は開放にしておきます。 [AY-3-8913] |

|||||||||||||||

| 13 | Vcc(+5V) | - | 電源端子です。 +5Vの電源を用意してください。 [AY-3-8913] |

|||||||||||||||

| 14 | TEST IN | I? | テスト用端子です。 詳細不明です。 通常は開放にしておきます。 [AY-3-8913] |

|||||||||||||||

| 15 | ANALOG CHANNEL B | O | チャンネルBのトーン出力端子です。 電流加算DACによる吐き出し電流出力と思われます。 他のチャンネルのトーン出力端子をそのまま接続してミキシングすることができます。 内部の出力部は15個のNchMOSFETをパラレル接続し、16段階の音量値ごとにドライブするMOSFETを選択しているようです。 対象のMOSFETがONした時に流れる電流値が 他のMOSFETがONした時に流れる電流値と異なるように設計されています。 この15個のMOSFETのドレインはVddに接続されています。 ソースが出力となっているので、出力電圧の状態によってはDACの直線性が悪くなる可能性があります。 ですので、AY-3-8910のデータシート内のFig.6のようなオペアンプを使ったI/V変換をすると良いでしょう。 AY-3-8913の場合、Fig.6の回路の最大出力電流は2000μAとなります。 [AY-3-8913] |

|||||||||||||||

| 16 | N.C. | - | 未接続 [AY-3-8913] |

|||||||||||||||

| 17 | ANALOG CHANNEL A | O | チャンネルAのトーン出力端子です。 15番ピンの「ANALOG CHANNEL B」に説明があるので、そちらを参照してください。 [AY-3-8913] |

|||||||||||||||

| 18 | ANALOG CHANNEL C | O | チャンネルAのトーン出力端子です。 15番ピンの「ANALOG CHANNEL B」に説明があるので、そちらを参照してください。 [AY-3-8913] |

|||||||||||||||

| 19 | Vss(GND) | - | グランド端子です。 [AY-3-8913] |

|||||||||||||||

| 20 | CLOCK | I | マスタークロック入力端子です。 最低1MHz、最大で2.5MHzまでのクロックを入力できます。 AY-3-8910とAY-3-8912は最大で2MHzまでのクロックを入力できます。 [AY-3-8913] |

|||||||||||||||

| 21 | ~RESET | I | リセット端子です。 この端子がLの期間、内部レジスタを初期化します。 この端子にはプルアップ抵抗が内蔵されています。 [AY-3-8913] |

|||||||||||||||

| 22 | ~A9 | I | チップセレクト端子です。 この端子がL かつ 24番ピンの「~CHIP SELECT」がL かつ 23番ピンの「A8」がHの期間に、2番ピンの「BDIR」の説明にある条件の時、内部のレジスタに対して書き込み・読み込みができます。 この端子にはプルダウン抵抗が内蔵されています。 [AY-3-8913] |

|||||||||||||||

| 23 | A8 | I | チップセレクト端子です。 この端子がH かつ24番ピンの「~CHIP SELECT」がL かつ 22番ピンの「~A9」がLの期間に、2番ピンの「BDIR」の説明にある条件の時、内部のレジスタに対して書き込み・読み込みができます。 この端子にはプルアップ抵抗が内蔵されています。 [AY-3-8913] |

|||||||||||||||

| 24 | ~CHIP SELECT | I | チップセレクト端子です。 この端子がL かつ 22番ピンの「~A9」がL かつ 23番ピンの「A8」がHの期間に、2番ピンの「BDIR」の説明にある条件の時、内部のレジスタに対して書き込み・読み込みができます。 この端子にはプルダウン抵抗が内蔵されています。 [AY-3-8913] |

・YM2149

| ピン番号 | 名称 | I/O | 機能 | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | Vss(GND) | - | グランド端子です。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 2 | N.C. | - | 未接続 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 3 | ANALOG CHANNEL B | O | チャンネルBのトーン出力端子です。 AY-3-8910と同様、電流加算DACによる吐き出し電流出力と思われます。 他のチャンネルのトーン出力端子をそのまま接続してミキシングすることができます。 AY-3-8910と同様なのかは不明ですが、出力電圧の状態によってはDACの直線性が悪くなる可能性があります。 AY-3-8910のデータシート内のFig.6のようなオペアンプを使ったI/V変換をすると良いでしょう。 ミキシングなしで1kΩの抵抗のみでI/V変換した場合、最大出力電圧は0.96~1.35Vになります。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 4 | ANALOG CHANNEL A | O | チャンネルAのトーン出力端子です。 3番ピンの「ANALOG CHANNEL B」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 5 | N.C. | - | 未接続 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 6 | IOB7 | I/O | 汎用I/Oポート端子です。 レジスタ$7のbit7「IOB」が0のとき入力、1のとき出力となります。 このポートが入力に設定されているとき、レジスタ$Fの対象ビットにこの端子の状態がセットされます。 このポートが出力に設定されているとき、レジスタ$Fの対象ビットの状態がこの端子に反映されます。 これらの端子にはプルアップ抵抗が内蔵されています。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 7 | IOB6 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 8 | IOB5 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 9 | IOB4 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 10 | IOB3 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 11 | IOB2 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 12 | IOB1 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 13 | IOB0 | I/O | 汎用I/Oポート端子です。 6番ピンの「IOB7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 14 | IOA7 | I/O | 汎用I/Oポート端子です。 レジスタ$7のbit6「IOA」が0のとき入力、1のとき出力となります。 このポートが入力に設定されているとき、レジスタ$Eの対象ビットにこの端子の状態がセットされます。 このポートが出力に設定されているとき、レジスタ$Eの対象ビットの状態がこの端子に反映されます。 これらの端子にはプルアップ抵抗が内蔵されています。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 15 | IOA6 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 16 | IOA5 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 17 | IOA4 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 18 | IOA3 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 19 | IOA2 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 20 | IOA1 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 21 | IOA0 | I/O | 汎用I/Oポート端子です。 14番ピンの「IOA7」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 22 | CLOCK | I | マスタークロック入力端子です。 26番ピンの「~SEL」がHもしくは開放のとき、 最低1MHz、最大で2MHzまでのクロックを入力できます。 26番ピンの「~SEL」がLのとき、 最低1MHz、最大で4MHzまでのクロックを入力できます。 内部にある分周器より、CLOCKに入力されたクロックの周波数の半分の周波数のクロックが使用されます。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 23 | ~RESET | I | リセット端子です。 この端子がLの期間、内部レジスタを初期化します。 この端子にはプルアップ抵抗が内蔵されています。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 24 | ~A9 | I | チップセレクト端子です。 この端子がLかつ25番ピンの「A8」がHの期間に、27番ピンの「BDIR」の説明にある条件の時、内部のレジスタに対して書き込み・読み込みができます。 この端子にはプルダウン抵抗が内蔵されています。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 25 | A8 | I | チップセレクト端子です。 この端子がHかつ24番ピンの「~A9」がLの期間に、27番ピンの「BDIR」の説明にある条件の時、内部のレジスタに対して書き込み・読み込みができます。 この端子にはプルアップ抵抗が内蔵されています。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 26 | ~SEL | I | クロック周波数選択端子です。 この端子がHまたは開放の時、22番ピンの「CLOCK」に入力できる最大クロック周波数は2MHzとなります。 この時、AY-3-8910と同様の音程となります。 この端子がLの時、22番ピンの「CLOCK」に入力できる最大クロック周波数は4MHzとなります。 内部にある分周器より、CLOCKに入力されたクロックの周波数の半分の周波数のクロックがシステムクロックとして使用されます。 この端子にはプルアップ抵抗が内蔵されています。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 27 | BDIR | I | バスコントロール端子です。 28番ピンの「BC2」と29番ピンの「BC1」とともに使用します。 25番ピンの「A8」がHかつ24番ピンの「~A9」がLの場合に以下の操作ができます。

[YM2149] |

||||||||||||||||||||||||||||||||||||

| 28 | BC2 | I | バスコントロール端子です。 27番ピンの「BDIR」と29番ピンの「BC1」とともに使用します。 27番ピンの「BDIR」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 29 | BC1 | I | バスコントロール端子です。 27番ピンの「BDIR」と28番ピンの「BC2」とともに使用します。 27番ピンの「BDIR」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 30 | DA7 | I/O | データ・アドレスバス端子です。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 31 | DA6 | I/O | データ・アドレスバス端子です。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 32 | DA5 | I/O | データ・アドレスバス端子です。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 33 | DA4 | I/O | データ・アドレスバス端子です。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 34 | DA3 | I/O | データ・アドレスバス端子です。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 35 | DA2 | I/O | データ・アドレスバス端子です。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 36 | DA1 | I/O | データ・アドレスバス端子です。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 37 | DA0 | I/O | データ・アドレスバス端子です。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 38 | ANALOG CHANNEL C | O | チャンネルCのトーン出力端子です。 3番ピンの「ANALOG CHANNEL B」に説明があるので、そちらを参照してください。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 39 | TEST 1 | O | テスト用端子です。 詳細不明です。 通常は開放にしておきます。 [YM2149] |

||||||||||||||||||||||||||||||||||||

| 40 | Vcc(+5V) | - | 電源端子です。 +5Vの電源を用意してください。 [YM2149] |

・YMZ284

| ピン番号 | 名称 | I/O | 機能 |

|---|---|---|---|

| 1 | ~WR | I | ライト端子です。 この端子がLでかつ、「~CS」がLの期間、 D0~D7端子の状態が内部レジスタへラッチされます。 [YMZ284] |

| 2 | ~CS | I | チップセレクト端子です。 この端子がLの期間に1番ピンの「~WR」端子がLの時、内部のレジスタに対して書き込みができます。 [YMZ284] |

| 3 | A0 | I | アドレス / データセレクト端子です。 この端子がLの場合、アドレス書き込みモードとなります。 DA0~DA7端子からデータを読み取り、内部のアドレス指定レジスタへ書き込みます。 この端子がHの場合、データ書き込みモードとなります。 DA0~DA7端子からデータを読み取り、アドレス指定レジスタで指定したレジスタに書き込みます。 [YMZ284] |

| 4 | VDD(+5V) | - | 電源端子です。 +5Vの電源を用意してください。 [YMZ284] |

| 5 | SO | O | トーン出力端子です。 3チャンネル分の出力がミキシングされたものが出力されます。 AY-3-8910と同様な電流加算DACかどうかは不明です。 一応、電流加算DACみたいな素振りはありそう? 各チャンネルの出力は、1kΩを介してこの端子へ接続されているかもしれません。(未検証) SO - GND 間に1kΩの抵抗を接続した場合、この端子から出力される最大出力振幅電圧は1.50~1.90Vになります。 [YMZ284] |

| 6 | GND | - | グランド端子です。 [YMZ284] |

| 7 | ΦM | I | マスタークロック入力端子です。 最低1MHz、最大で4MHzまでのクロックを入力できます。 内部にある分周器より、CLOCKに入力されたクロックの周波数の半分の周波数のクロックがシステムクロックとして使用されます。 [YMZ284] |

| 8 | ~IC | I | リセット端子です。 この端子がLの期間、内部レジスタを初期化します。 この端子にはプルアップ抵抗が内蔵されています。 [YMZ284] |

| 9 | D7 | I/O | データ・アドレスバス端子です。 [YMZ284] |

| 10 | D6 | I/O | データ・アドレスバス端子です。 [YMZ284] |

| 11 | D5 | I/O | データ・アドレスバス端子です。 [YMZ284] |

| 12 | D4 | I/O | データ・アドレスバス端子です。 [YMZ284] |

| 13 | D3 | I/O | データ・アドレスバス端子です。 [YMZ284] |

| 14 | D2 | I/O | データ・アドレスバス端子です。 [YMZ284] |

| 15 | D1 | I/O | データ・アドレスバス端子です。 [YMZ284] |

| 16 | D0 | I/O | データ・アドレスバス端子です。 [YMZ284] |

・YMZ294

| ピン番号 | 名称 | I/O | 機能 |

|---|---|---|---|

| 1 | ~WR | I | ライト端子です。 この端子がLでかつ、「~CS」がLの期間、 D0~D7端子の状態が内部レジスタへラッチされます。 [YMZ294] |

| 2 | ~CS | I | チップセレクト端子です。 この端子がLの期間に1番ピンの「~WR」端子がLの時、内部のレジスタに対して書き込みができます。 [YMZ294] |

| 3 | A0 | I | アドレス / データセレクト端子です。 この端子がLの場合、アドレス書き込みモードとなります。 DA0~DA7端子からデータを読み取り、内部のアドレス指定レジスタへ書き込みます。 この端子がHの場合、データ書き込みモードとなります。 DA0~DA7端子からデータを読み取り、アドレス指定レジスタで指定したレジスタに書き込みます。 [YMZ294] |

| 4 | VDD(+5V) | - | 電源端子です。 +5Vの電源を用意してください。 [YMZ294] |

| 5 | SO | O | トーン出力端子です。 3チャンネル分の出力がミキシングされたものが出力されます。 AY-3-8910と同様な電流加算DACかどうかは不明です。 一応、電流加算DACみたいな素振りはありそう? 各チャンネルの出力は、1kΩを介してこの端子へ接続されているかもしれません。(未検証) SO - GND 間に1kΩの抵抗を接続した場合、この端子から出力される最大出力振幅電圧は1.50~1.90Vになります。 [YMZ294] |

| 6 | GND | - | グランド端子です。 [YMZ294] |

| 7 | ΦM | I | マスタークロック入力端子です。 8番ピンの「4/6」がHのとき、 標準で4MHzのクロックを入力します。 内部にある分周器より、CLOCKに入力されたクロックの周波数の半分の周波数のクロックがシステムクロックとして使用されます。 8番ピンの「4/6」がLのとき、 標準で6MHzのクロックを入力します。 内部にある3分周器より、CLOCKに入力されたクロックの周波数の1/3の周波数のクロックがシステムクロックとして使用されます。 [YMZ294] |

| 8 | 4/6 | I | クロック周波数選択端子です。 この端子がHの時、7番ピンの「ΦM」に入力する標準クロック周波数は4MHzとなります。 内部にある分周器より、ΦMに入力されたクロックの周波数の半分の周波数のクロックがシステムクロックとして使用されます。 この端子がLの時、7番ピンの「ΦM」に入力する標準クロック周波数は6MHzとなります。 内部にある3分周器より、ΦMに入力されたクロックの周波数の1/3の周波数のクロックがシステムクロックとして使用されます。 [YMZ294] |

| 9 | ~IC | I | リセット端子です。 この端子がLの期間、内部レジスタを初期化します。 この端子にはプルアップ抵抗が内蔵されています。 [YMZ294] |

| 10 | ~TEST | I | テスト用端子です。 詳細不明です。 通常は開放にしておきます。 [YMZ294] |

| 11 | D7 | I/O | データ・アドレスバス端子です。 [YMZ294] |

| 12 | D6 | I/O | データ・アドレスバス端子です。 [YMZ294] |

| 13 | D5 | I/O | データ・アドレスバス端子です。 [YMZ294] |

| 14 | D4 | I/O | データ・アドレスバス端子です。 [YMZ294] |

| 15 | D3 | I/O | データ・アドレスバス端子です。 [YMZ294] |

| 16 | D2 | I/O | データ・アドレスバス端子です。 [YMZ294] |

| 17 | D1 | I/O | データ・アドレスバス端子です。 [YMZ294] |

| 18 | D0 | I/O | データ・アドレスバス端子です。 [YMZ294] |

・PSG・SSGのレジスタ(書き込み専用)

PSG・SSGは$0~$Fの16バイト分のレジスタを持っています。

| アドレス |

レジスタ名 | 機能 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| $0 | Channel A Tone Period | チャンネルAの音程設定レジスタです。 $1とセットで使用します。

TP: TONE PERIOD 音程設定ビットです。 $1にあるTP_A_11~TP_A_8とセットで使用します。 TP = 1 ~ 4095 (0x001 ~ 0xFFF) : 音程設定ビット この値が大きいほど、低い音程の音が出力されます。 レジスタ設定値と出力周波数foutは以下の関係があります。 TP = fsc / (16 * fout) レジスタ設定値から出力周波数を求めたい場合は以下のとおりです。 fout = fsc / (16 * TP) [Hz] TP : 音程設定ビット(12bit) fsc : システムクロック周波数[Hz] 各PSG・SSGのシステムクロック周波数は次のとおりです。 fsc = ΦM [AY-3-8910、AY-3-8912、AY-3-8913、YM2149(~SEL=H)] fsc = ΦM / 2 [YM2149(~SEL=L)、YMZ284、YMZ294(~SEL=H)] fsc = ΦM / 3 [YMZ294(~SEL=L)] ΦM : 入力クロック周波数[Hz] --MIDIノートナンバーからレジスタ値を求める場合-- TP = fsc / (16 * (440 / 2^(69/12)) * 2^(note_n/12)) = fsc / (16 * 8.1758 * 2^(note_n/12)) = fsc / (130.81 * 2^(note_n/12)) note_n : MIDIノートナンバ(0~127、note_n=69のときfout=440) [システムクロックfsc = 2MHzの場合] TP = fsc / (130.81 * 2^(note_n/12)) = 2M / (130.81 * 2^(note_n/12)) = 15289 / 2^(note_n/12) |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $1 | Channel A Tone Period | チャンネルAの音程設定レジスタです。 $0とセットで使用します。

$0に説明があるので、そちらを参照してください。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $2 | Channel B Tone Period | チャンネルBの音程設定レジスタです。 $3とセットで使用します。

音程の指定方法は$0の「Channel A Tone Period」と同様なので、そちらを参照してください。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $3 | Channel B Tone Period | チャンネルBの音程設定レジスタです。 $2とセットで使用します。

音程の指定方法は$0の「Channel A Tone Period」と同様なので、そちらを参照してください。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $4 | Channel C Tone Period | チャンネルCの音程設定レジスタです。 $3とセットで使用します。

音程の指定方法は$0の「Channel A Tone Period」と同様なので、そちらを参照してください。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $5 | Channel C Tone Period | チャンネルCの音程設定レジスタです。 $2とセットで使用します。

音程の指定方法は$0の「Channel A Tone Period」と同様なので、そちらを参照してください。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $6 | Noise Period | ノイズ音程設定レジスタです。

NP: NOISE PERIOD ノイズ周波数設定ビットです。 NP = 0 ~ 31 (0x00 ~ 0x1F) : ノイズ周波数設定ビット この値が大きいほど、低いノイズ周波数の音が出力されます。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $7 | ~Enable | ミキサ設定 / I/O方向設定レジスタです。

IO_B(bit7): 汎用ポートBの方向設定ビットです。 このレジスタはAY-3-8910、YM2149の場合に使用します。 IO_B = H : ポートBを出力に設定します。 IO_B = L : ポートBを入力に設定します。 IO_A(bit6): 汎用ポートAの方向設定ビットです。 このレジスタはAY-3-8910、AY-3-8912、YM2149の場合に使用します。 IO_A = H : ポートAを出力に設定します。 IO_A = L : ポートAを入力に設定します。 NE_C(bit5)、NE_B(bit4)、NE_A(bit3): チャンネルごとのノイズ出力設定ビットです。 NE_C = H : ノイズ出力先としてチャンネルCを設定しません。 NE_C = L : ノイズ出力先としてチャンネルCを設定します。 NE_B = H : ノイズ出力先としてチャンネルBを設定しません。 NE_B = L : ノイズ出力先としてチャンネルBを設定します。 NE_A = H : ノイズ出力先としてチャンネルAを設定しません。 NE_A = L : ノイズ出力先としてチャンネルAを設定します。 TE_C(bit2)、TE_B(bit1)、TE_A(bit0): トーンの出力設定ビットです。 TE_C = H : チャンネルCのトーン出力を無効に設定します。 TE_C = L : チャンネルCのトーン出力を有効に設定します。 TE_B = H : チャンネルBのトーン出力を無効に設定します。 TE_B = L : チャンネルBのトーン出力を有効に設定します。 TE_A = H : チャンネルAのトーン出力を無効に設定します。 TE_A = L : チャンネルAのトーン出力を有効に設定します。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $8 | Channel A Amplitude | チャンネルAの音量設定レジスタです。

M_A(bit4): チャンネルA音量モード選択ビットです。 固定音量かエンベロープジェネレータによる音量制御をするかを選べます。 固定に設定した場合、音量は$8「Channel A Amplitude」のbit3~0のL_Aの値により決まります。 エンベロープジェネレータに設定した場合、レジスタ値による音量制御はできないので注意してください。 M_A = L : $8「Channel A Amplitude」のbit3~0のL_Aの値により、チャンネルAの音量が決まります。 M_A = H : エンベロープジェネレータにより、チャンネルAの音量が決まります。 L_A(bit3 ~ bit0): チャンネルA音量設定ビットです。 上記$8「Channel A Amplitude」のbit4のM_AがLのとき、このレジスタの値がチャンネルAの出力音量となります。 この値が大きいほど、音量が大きくなります。 音量に対するレジスタ値は直線対数の関係となります。 L_A = 0 ~ 15 (0x0 ~ 0xF) : チャンネルA音量設定ビット レジスタ値L_Aに対する音量比Lvは、 Lv = 2 ^ ((L_A - 15) / 2) (L_A ≠ 0) Lv = 0 (L_A = 0) となります。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $9 | Channel B Amplitude | チャンネルBの音量設定レジスタです。

M_B(bit4): チャンネルB音量モード選択ビットです。 固定音量かエンベロープジェネレータによる音量制御をするかを選べます。 固定に設定した場合、音量は$9「Channel B Amplitude」のbit3~0のL_Bの値により決まります。 エンベロープジェネレータに設定した場合、レジスタ値による音量制御はできないので注意してください。 M_B = L : $9「Channel B Amplitude」のbit3~0のL_Bの値により、チャンネルBの音量が決まります。 M_B = H : エンベロープジェネレータにより、チャンネルBの音量が決まります。 L_B(bit3 ~ bit0): チャンネルB音量設定ビットです。 上記$9「Channel B Amplitude」のbit4のM_BがLのとき、このレジスタの値がチャンネルBの出力音量となります。 この値が大きいほど、音量が大きくなります。 音量に対するレジスタ値は直線対数の関係となります。 L_B = 0 ~ 15 (0x0 ~ 0xF) : チャンネルB音量設定ビット レジスタ値L_Bに対する音量比Lvは、 Lv = 2 ^ ((L_B - 15) / 2) (L_B ≠ 0) Lv = 0 (L_B = 0) となります。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $A | Channel C Amplitude | チャンネルCの音量設定レジスタです。

M_C(bit4): チャンネルC音量モード選択ビットです。 固定音量かエンベロープジェネレータによる音量制御をするかを選べます。 固定に設定した場合、音量は$A「Channel C Amplitude」のbit3~0のL_Cの値により決まります。 エンベロープジェネレータに設定した場合、レジスタ値による音量制御はできないので注意してください。 M_C = L : $A「Channel C Amplitude」のbit3~0のL_Cの値により、チャンネルCの音量が決まります。 M_C = H : エンベロープジェネレータにより、チャンネルCの音量が決まります。 L_C(bit3 ~ bit0): チャンネルC音量設定ビットです。 上記$A「Channel C Amplitude」のbit4のM_CがLのとき、このレジスタの値がチャンネルCの出力音量となります。 この値が大きいほど、音量が大きくなります。 音量に対するレジスタ値は直線対数の関係となります。 L_C = 0 ~ 15 (0x0 ~ 0xF) : チャンネルC音量設定ビット レジスタ値L_Cに対する音量比Lvは、 Lv = 2 ^ ((L_C - 15) / 2) (L_C ≠ 0) Lv = 0 (L_C = 0) となります。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $B | Envelope Period | エンベロープ周波数設定レジスタです。 $Cとセットで使用します。

EP: ENVELOPE PERIOD エンベロープ周波数設定ビットです。 $CにあるEP_15~EP_8とセットで使用します。 EP = 1 ~ 65535 (0x0001 ~ 0xFFFF) : エンベロープ周波数設定ビット この値が大きいほど、長い周期のエンベロープ波形となります。 レジスタ設定値とエンベロープ周波数f_evは以下の関係があります。 EP = fsc / (256 * f_ev) レジスタ設定値からエンベロープ周波数を求めたい場合は以下のとおりです。 f_ev = fsc / (256 * TP) [Hz] fsc : システムクロック [Hz] システムクロックfscについては$0の「Channel A Tone Period」で説明しているので、そちらを参照してください。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $C | Envelope Period | エンベロープ周波数設定レジスタです。 $Bとセットで使用します。

$Bに説明があるので、そちらを参照してください。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $D | Envelope Shape Cycle | エンベロープ波形コントロール設定レジスタです。

以下のレジスタビット説明は挙動に基づく説明であり、実際の内部回路とは異なります。 CONT(bit3): ・COUT=Lのとき エンベロープ周期の最後に到達すると、エンベロープカウンタが停止して出力音量が0になります。 ・COUT=Hのとき エンベロープ周期の最後に到達してもエンベロープカウンタは停止しません。 ATT(bit2): ・ATT=Lのとき エンベロープ周期の先頭でエンベロープカウンタを最大値に初期化します。 エンベロープカウンタはデクリメント設定となります。 ・ATT=Hのとき エンベロープ周期の先頭でエンベロープカウンタを0に初期化します。 エンベロープカウンタはインクリメント設定となります。 ALT(bit1): ・ALT=Lのとき エンベロープカウンタの値がそのまま音量となります。 ・ALT=Hのとき エンベロープ周期の最後に到達するごとに、エンベロープカウンタの最大値と最小値の関係を逆転させたものを音量とします。(エンベロープカウンタそのものの値が逆転するわけではありません。) HOLD(bit0): ・HOLD=Lのとき エンベロープ周期の最後に到達した時、エンベロープカウンタをATTで指定した初期値で初期化します。 ・HOLD=Hのとき エンベロープ周期の最後に到達した時、エンベロープカウンタが停止します。

上記4つの設定をまとめると、エンベロープ形状は以下のようになります。

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $E | I/O Port A Data Store | 汎用ポートAレジスタです。

IOA: 汎用ポートAレジスタです。 AY-3-8910、AY-3-8912、YM2149の場合、このレジスタを使用します。 $7の「~Enable」のbit6 IO_AがLの時、汎用ポートAは入力モードになります。 IO_AがHの時、汎用ポートAは出力モードとなります。 AY-3-8910、YM2149の場合 入力モードの場合、21番ピンの「IOA0」から14番ピンの「IOA7」までのポートの状態がこのレジスタへセットされます。 出力モードの場合、このレジスタの内容が21番ピンの「IOA0」から14番ピンの「IOA7」に反映されます。 AY-3-8912の場合 入力モードの場合、14番ピンの「IOA0」から7番ピンの「IOA7」までのポートの状態がこのレジスタへセットされます。 出力モードの場合、このレジスタの内容が14番ピンの「IOA0」から7番ピンの「IOA7」に反映されます。 AY-3-8913、YMZ284、YMZ294の場合 汎用ポートAが無いため、このレジスタに対して読み書きした時の挙動は不明です。 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| $F | I/O Port B Data Store [YMZ284の場合 YMZ294の場合は不明] Control Power |

[AY-3-8910、AY-3-8912、AY-3-8913、YM2149] 汎用ポートBレジスタです。

IOB: 汎用ポートBレジスタです。 AY-3-8910、YM2149の場合、このレジスタを使用します。 $7の「~Enable」のbit7 IO_BがLの時、汎用ポートBは入力モードになります。 IO_BがHの時、汎用ポートBは出力モードとなります。 AY-3-8910、YM2149の場合 入力モードの場合、13番ピンの「IOB0」から6番ピンの「IOB7」までのポートの状態がこのレジスタへセットされます。 出力モードの場合、このレジスタの内容が13番ピンの「IOB0」から6番ピンの「IOB7」に反映されます。 AY-3-8913の場合 汎用ポートBが無いため、このレジスタに対して読み書きした時の挙動は不明です。 YMZ284、YMZ294の場合 YMZ284の場合、このレジスタアドレスは「Control Power」として割り当てられています。

YMZ284のデータシートにはこのレジスタについての機能は説明しておらず、bit7~bit4にはすべてLを書き込むよう記述があります。 YMZ294の場合は不明ですが、YMZ284と同様にこのレジスタアドレスには「Control Power」が割り当てられている可能性が高いと思います。 |

レジスタマップ

内部レジスタのレジスタマップ(ビットマップ)です。

"レジスタビット名"_"ビット名またはチャンネルNO."_"第何ビット"

の形で表しています。

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | |

|---|---|---|---|---|---|---|---|---|

| $0 | TP_A_7 | TP_A_6 | TP_A_5 | TP_A_4 | TP_A_3 | TP_A_2 | TP_A_1 | TP_A_0 |

| $1 | - | - | - | - | TP_A_11 | TP_A_10 | TP_A_9 | TP_A_8 |

| $2 | TP_B_7 | TP_B_6 | TP_B_5 | TP_B_4 | TP_B_3 | TP_B_2 | TP_B_1 | TP_B_0 |

| $3 | - | - | - | - | TP_B_11 | TP_B_10 | TP_B_9 | TP_B_8 |

| $4 | TP_C_7 | TP_C_6 | TP_C_5 | TP_C_4 | TP_C_3 | TP_C_2 | TP_C_1 | TP_C_0 |

| $5 | TP_C_11 | TP_C_10 | TP_C_9 | TP_C_8 | ||||

| $6 | - | - | - | NP_4 | NP_3 | NP_2 | NP_1 | NP_0 |

| $7 | IO_B | IO_A | NE_C | NE_B | NE_A | TE_C | TE_B | TE_A |

| $8 | - | - | - | M_A | L_A_3 | L_A_2 | L_A_1 | L_A_0 |

| $9 | - | - | - | M_B | L_B_3 | L_B_2 | L_B_1 | L_B_0 |

| $A | - | - | - | M_C | L_C_3 | L_C_2 | L_C_1 | L_C_0 |

| $B | EP_7 | EP_6 | EP_5 | EP_4 | EP_3 | EP_2 | EP_1 | EP_0 |

| $C | EP_15 | EP_14 | EP_13 | EP_12 | EP_11 | EP_10 | EP_9 | EP_8 |

| $D | - | - | - | - | CONT | ATT | ALT | HOLD |

| $E | IOA_7 | IOA_6 | IOA_5 | IOA_4 | IOA_3 | IOA_2 | IOA_1 | IOA_0 |

| $F | IOB_7 ※CP3 |

IOB_6 ※CP2 |

IOB_5 ※CP1 |

IOB_4 ※CP0 |

IOB_3 | IOB_2 | IOB_1 | IOB_0 |

※YMZ284、YMZ294?の場合

・タイミング図

AY-3-8910、AY-3-8912、AY-3-8913、YM2149へのアドレス書き込みタイミング

BC2の入力をHに固定した場合のアドレス書き込みタイミングです。

AY-3-8910、AY-3-8912、AY-3-8913、YM2149へのデータ書き込みタイミング

BC2の入力をHに固定した場合のデータ書き込みタイミングです。上記図では、AY-3-891XとYM2149のどちらも満たすタイミングとなっています。

AY-3-8910、AY-3-8912、AY-3-8913、YM2149からのデータ読み取りタイミング

BC2の入力をHに固定した場合のアドレス読み取りタイミングです。

上記図では、AY-3-891XとYM2149のどちらも満たすタイミングとなっています。

AY-3-8910、AY-3-8912、AY-3-8913、YM2149のレジスタへ値をセットする

上記のタイミングどおりアドレス書き込み後、データを書き込むことで内部のレジスタへ反映されます。

ビジーフラグなどはありません。

YMZ284、YMZ294へのアドレス・書き込みタイミング

A0端子がLの場合、書き込み先アドレスを内部レジスタへセットします。

A0端子がHの場合、指定したアドレスにデータをセットします。

・使い方(制御)

PSG・SSGのレジスタは、大まかに分けて3種類あります。

このうち、I/O関係のレジスタは一部のICをのぞいて発音に影響しません。

発音関係のレジスタ

・矩形波周波数設定レジスタ(12bit)

・ノイズ周波数設定レジスタ(5bit)

・エンベロープ有効無効・音量設定レジスタ(5bit)・ミキサー設定レジスタ(6bit)

エンベロープ関係のレジスタ

・エンベロープ周波数設定レジスタ(16bit)

・エンベロープコントロールレジスタ(4bit)I/O関係のレジスタ

・I/O設定レジスタ(2bit)

・I/Oポートレジスタ(16bit)

※SSGLとSSGLPの$Fには「Control Power」が割り当てられているので注意

・発音手順

--PSG・SSGのリセット直後からの基本的な発音手順--

①ミキサー設定レジスタで出力する発音チャンネルを設定する。

エンベロープを有効にする場合は、エンベロープ周波数設定レジスタやエンベロープコントロールレジスタの設定もする。

②矩形波周波数設定レジスタに音程をセットする。

③エンベロープ有無または音量の設定値をエンベロープ有効無効・音量設定レジスタへセットし、発音させる。

①ミキサー設定レジスタで出力する発音チャンネルを設定する。

PSG・SSGのミキサー設定レジスタ「~Enable」($7)で各チャンネルの音の出力の有効無効を設定します。

出力チャンネルはA、B、Cの3つあり、トーンの音量やエンベロープ制御はチャンネルに対して効きます。

出力チャンネルはA、B、CにはそれぞれトーンA、トーンB、トーンCが出力されるのですが、このミキサー設定レジスタで音の出力の有効無効しなければいけません。

ノイズチャンネルは、出力チャンネルA、B、Cに対して音の出力の有効無効ができます。

音量やエンベロープが共用となるので注意してください。

基本的には、トーンA、トーンB、トーンCの出力を有効にしておきます。

②矩形波周波数設定レジスタに音程をセットする。

各チャンネルの矩形波周波数設定レジスタ「Channel X Tone Period」($0~$5)に発音したい音程を設定します。

1つのチャンネルあたりの設定できる値は12bit分(0~4095)あるため、2つのレジスタへわけられています。

③エンベロープ有無または音量の設定値をエンベロープ有効無効・音量設定レジスタへセットし、発音させる

各チャンネルの音量設定レジスタ「Channel X Amplitude」($8~$A)

に発音したいチャンネルの音量を設定します。

このレジスタのbit4「M_X」(XはA,B,Cのいづれか)がLの場合、

このレジスタのbit0~bit3の値によって音量が決定します。

bit4「M_X」がHの場合、エンベロープジェネレータで生成された音量値が自動で設定されます。

エンベロープジェネレータが出力する音量値は、3チャンネル共通となっています。

コードの発音などの同時発音の場合は問題ありませんが、チャンネルごと異なるキーオンの場合任意のエンベロープ波形が得られません。

制御側のMCUの処理能力に余裕がある場合は、PSG、SSGのハードウェアエンベロープを無効にして、MCU側で逐次音量制御するソフトウェアエンベロープ制御を行うと各チャンネル毎に任意のエンベロープ波形が得られます。

後ほど紹介する使用例では、マイコン側で音量制御するソフトウェアエンベロープとなっています。

・使い方(回路)

PSG(AY-3-891X)の最大消費電流は85mAであり、通電中はほんのり暖かくなります。

SSG(YM2149)の最大消費電流は40mAであり、PSGに比べて消費電力が小さいようです。

SSGC(YM3439)やSSGL(YMZ284)、SSGLP(YMZ294)はCMOS品であるため、ほとんど発熱しません。

USB駆動の場合は、SSGCやSSGL、SSGLPあたりがおすすめです。

・クロック

PSGやSSGのクロック源として基本的に2.00MHzまたは4.00MHzのクリスタルオシレータを使用します。

PSG(AY-3-891X)は2MHz、SSG(YM2149)とSSGC(YM3439)は2MHzまたは4MHz、

SSGL(YMZ284)は4MHz、SSGLP(YMZ294)は4MHzまたは6MHzが基本的なクロック周波数となっています。

ごちゃまぜで使いたい場合は、4MHzのクリスタルオシレータを用意してから分周して2MHzを得ると良いでしょう。

・バス制御信号

SSGLとSSGLPのバス制御信号は「~CS」、「~WR」、「A0」の現代的な制御方法なのですが、これ以外のものはCP1610用のバス制御信号となっているため、少し扱いにくいです。

ですが、「BC2」と「A8」をH、「~A9」を「~CS」、「BDIR」を「WR」、「BC1」を「~A0」とするとインバータ2個あれば現代的なバス制御信号で操作できます。(場合によってはうまくいかないかもしれません)

・サウンド出力周辺の回路

PSGやSSG、SSGCあたりは電流加算DACとなっており、複数のICやチャンネル出力を直にまとめて接続できます。

SSGLやSSGLPの出力部は不明ですが恐らく電流加算DACだと思います。

同じ設定音量でもSSGLやSSGLPの方が出力電流が大きく、単純にPSGやSSGと接続した場合、音量バランスが崩れます。

余談ですが、SSGP(YMZ261)やSSGP2(YMZ285)の場合、IC内部で出力部に1kΩの抵抗がGNDと接続されています。

PSGやSSGは、吐き出し型電流加算DACなのでI/V変換をしてあげなければいけません。

NMOSFETのソースが出力となっているので、出力電圧の状態によってはDACの直線性が悪くなる可能性があります。

オペアンプを使ったI/V変換回路を組むと、音源ICの出力端子の電圧を常に固定に出来るので、DACの直線性良くなると思います。

オペアンプを使ったI/V変換の欠点は負電圧の電源が必要になることでしょうか?

単電源で音を出したい時は、出力端子とGND間に抵抗を用意した簡易的なI/V変換を行う回路で済ます場合が多いです。

この場合、出力端子の電圧が2V~2.5Vより上がる(実験による値)と、急激に音量が歪みます。

ですので、音源ICを多数用意して出力どうしを直結した場合、出力抵抗を小さくする必要があります。目安として、1k/(音源ICの数)Ω 以下にすると良いでしょう。

左:オペアンプを使ったI/V変換(負電源が必要)

右:抵抗を使ったI/V変換

・全体の回路例

各音源ICごとの接続例です。

基本的には、1種類の音源ICを複数使うケースが多いと思いますが、せっかくなので様々な音源ICを同時に使える回路を紹介します。

同じ音源ICをたくさん使いたい場合は、該当する音源ICのチップセレクト(~CS0から~CS5)以外の回路を接続例と同じ接続にするとよいです。一個だけ使用したい場合は、その音源IC分だけ配線するとよいです。

バス制御信号はSSGLやSSGLPなどで使われている~WR、A0、~CSのタイミング図に則って制御すると、PSGやSSG、SSGP2なども同一のバス制御信号で音を出すことができます。

その逆(BDIR、BC1、BC2)の制御タイミングでは、SSGLやSSGLPで発音できないので注意してください。

しれっと回路図中にSSGP2(YMZ285)が入っていますが、この音源ICは本来内蔵シーケンサでのみ演奏できるもので、SSGのレジスタに外部から直接アクセスできません。

(秋月電子でかなり前から販売されていて、いわゆる「地雷枠」扱いされている不憫なICです。)

ですが調査の結果、テスト端子のTEST2のみLにすると、ICのテストモードに入ることができ、内部のSSGのレジスタに外部から直接アクセスできるようになることがわかりました。

TEST1=H、TEST2=Lにすると、SSGP2の5番ピン「/CS」と6番ピンの「/WR」がそれぞれ「WE」と「~A0」端子に変化します。(まだ詳しく調べてないので間違っているかもしれません)

(もう少し正確には、6番ピンがHの期間にデータバスの状態をアドレスとして取り込めるようになります。)

チップセレクトができなくなるため、少し使いにくいですがSSG音源ICとして使えるようになったのでいいとします。

SSGP2(YMZ285)の詳しい説明は後日まとめようと思います。

・各音源ICごと(1種類)の場合の回路

・PSG(AY-3-891X)、SSG(YM2149)、SSGC(YM3439)

後述するプログラム例の設定値

#define IC_NUM 8

unsigned char psg_type[IC_NUM] = {0, 0, 0, 0, 0, 0, 0, 0};

・SSGL(YMZ284)、SSGLP(YMZ294)

・SSGP2(YMZ285)

・SSGS3(YMZ771)

・使用例

プログラム例はページサイズの都合上、使用例は別のページにしています。

AY-3-8910(PSG)・SSG(YMZ294等)の使い方②

音源ICの使い方一覧へ

/*検索エンジン用単語リスト*/

sound generator

how to use

usage

0 件のコメント:

コメントを投稿